- 软件信息

- 同类热门

- 攻略推荐

简介

modelsim是一款功能十分强大的HDL语言仿真软件的,可以不敢住用户轻松完成编辑,重新编译、重新模拟等操作,满足打击对调试和仿真环境的专属需求。modelsim破解版的吸睛之处在于支持VHDL、Verilog、SystemVerilog等多种语言的混合使用,可以实现的功能会更加的丰富多彩,更加高效的完成各项模拟工作,有需要的朋友不要错过。

提取码:ifte

和老版本不同的是,modelsim 10.5进行了全面升级与改进操作,各方面的性能会有非常大的改进,并且能够全面支持业界广泛的标准,希望大家会喜欢。

modelsim破解版特色介绍:

非常知名的HDL语言仿真软件,提供友好的仿真环境;

支持VHDL和Verilog混合仿真的仿真器;

采用单一内核仿真技术,编译仿真速度快;

提供个性化的图形界面和用户接口;

RTL和门级优化,本地编译结构,跨平台跨版本仿真;

源代码模版和助手,项目管理;

对SystemC的直接支持和HDL任意混合;

可以单独或同时进行行为(behavioral)、RTL级、和门级(gate-level)的代码。

modelsim破解安装教程:

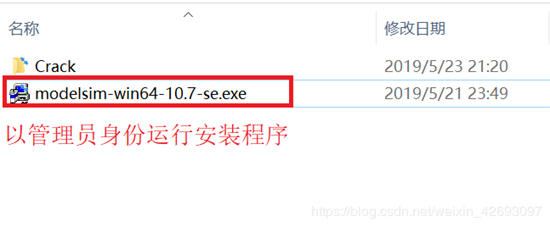

1.解压安装包。

2.以管理员身份运行安装程序。

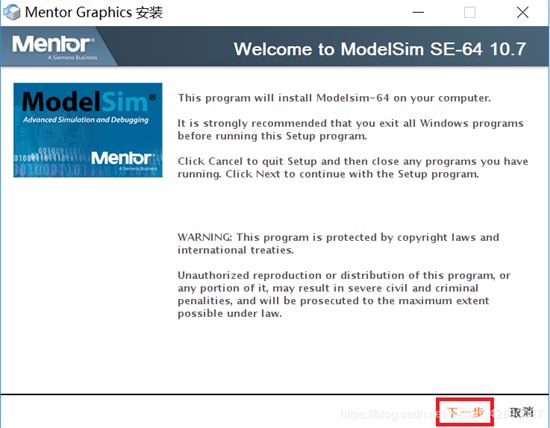

3.点击“下一步”。

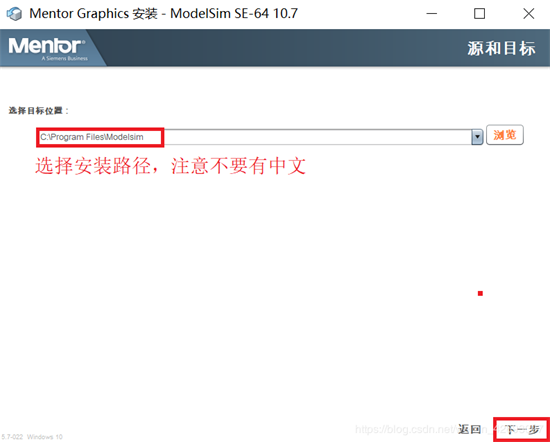

4.点击“下一步”。

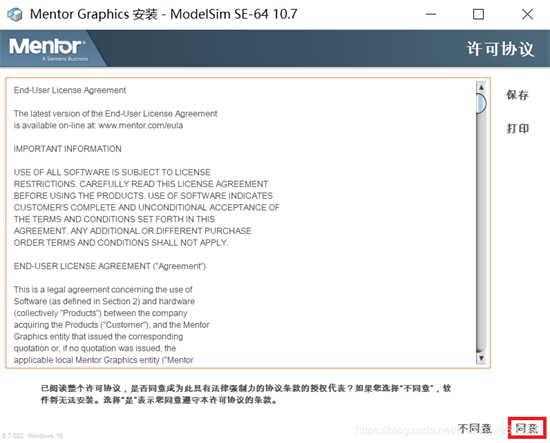

5.点击“同意”。

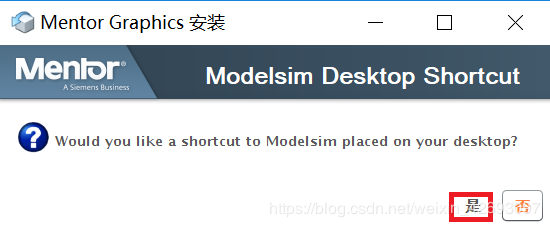

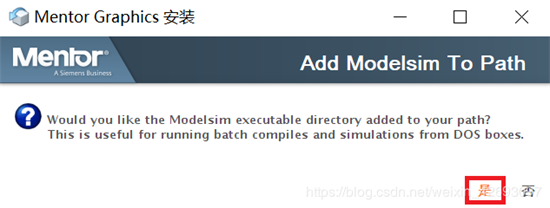

6.遇到如下窗口点击“是”。

7.遇到如下窗口点击“是”。

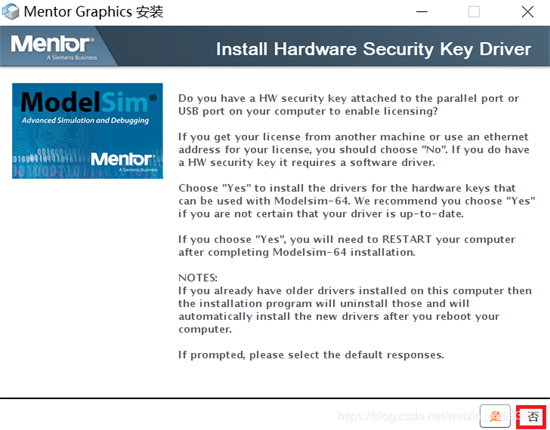

8.遇到如下窗口点击“否”(有的安装教程选择的“是”,这个应该影响不大)。

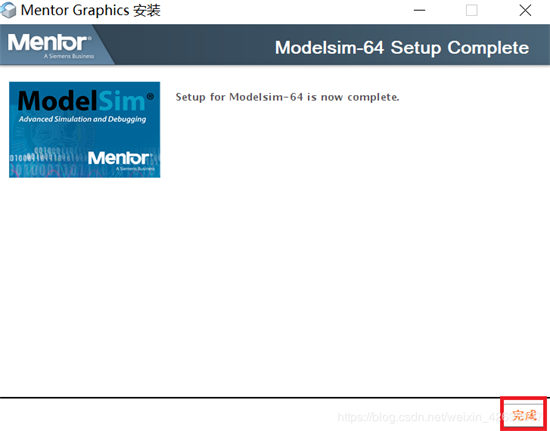

9.点击完成。

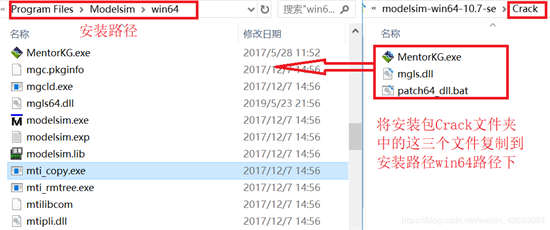

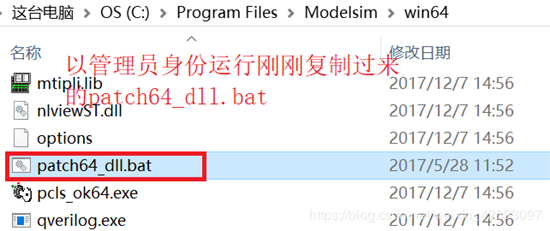

10.将安装包Crack文件夹中的这三个文件复制到安装目录win32/win64文件夹下面(如果win32/win64文件夹里面有mgls.dll文件,则mgls.dll不需要复制)。

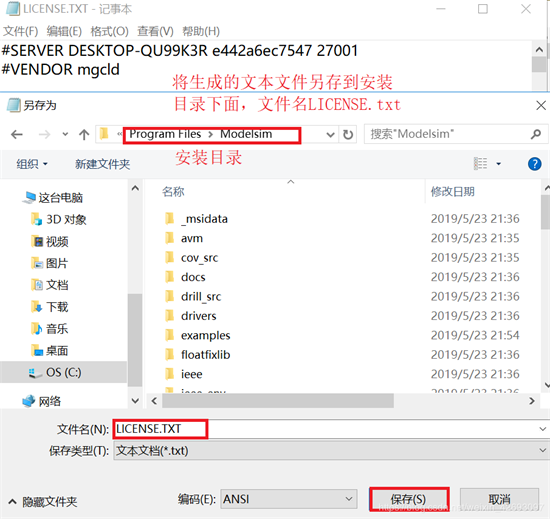

11.以管理员身份运行上面复制到安装路径的patch64_dll.bat,保存生成的LICENSE.TXT文件文件到安装目录下面,如我的保存的目录是C:\Program Files\Modelsim。

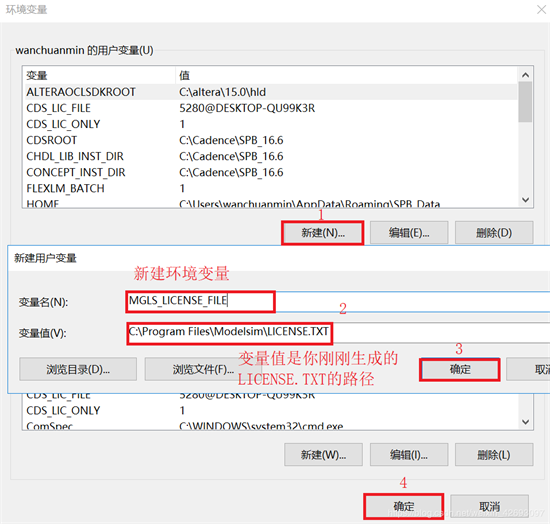

12.新建环境变量(环境变量在“我的电脑–属性–高级系统设置–环境变量”),变量名为MGLS_LICENSE_FILE,变量值为上面LICENSE.TXT文件的路径,如我的是C:\Program Files\Modelsim\LICENSE.TXT。

13.打开桌面Modelsim的快捷方式。

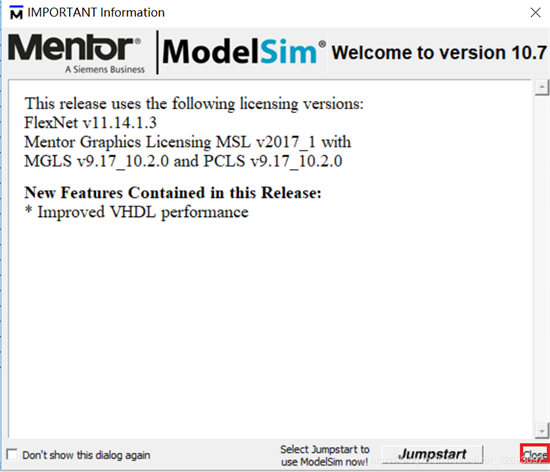

14.出现如下,点击“Close”。

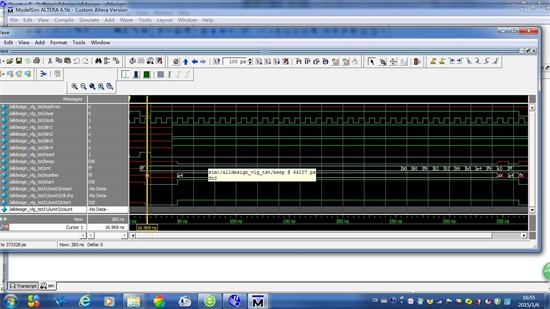

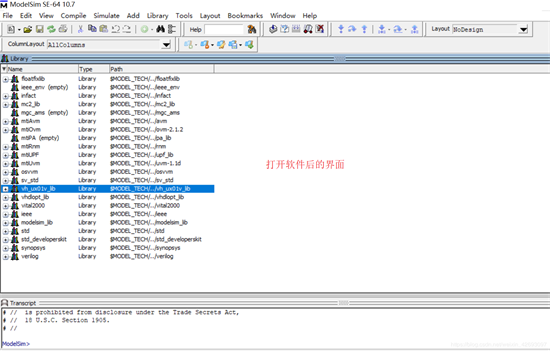

15.打开后的界面如上图所示。

modelsim仿真教程:

1. 新建工程

file->new->project,输入工程名 例如half_clk

2. 新建文件

新建二分频器模块文件和testbench文件,分别为half_clk和half_clk_tb,注意type选择Verilog。

3. 编写模块文件和激励文件内容

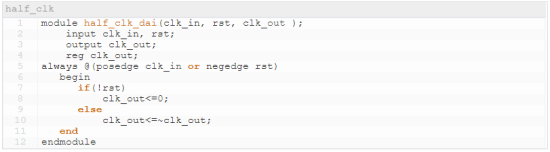

half_clk.v

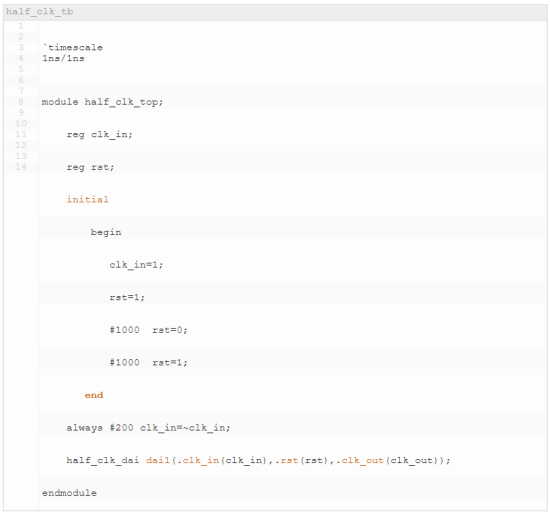

half_clk_tb.v

4. 编译文件

编译前一定注意要保存文件!! 【ctrl+s】

点击工具栏按钮,编译全部文件,如果文件名后的status显示√就表示没有语法错误,编译成功。

否则

如果有错误可以双击红色的error查看具体的错误信息。

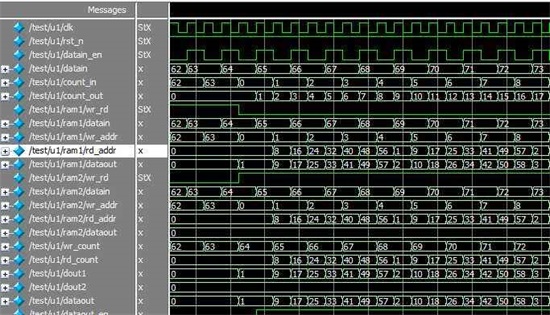

5. 工程仿真

点击工具栏的Simulation按钮进行仿真。

选择work->half_clk_top,因为只需要对testbench文件进行仿真就行,取消左下角的优化选项,因为可能会把object框里的信号量优化掉.

在 instance里显示了testbench的文件结构,有一个always和一个initial,调用的half_clk里有个一always循环。

在信号量上 右键->add > To Dataflow > Selected Items可以查看设计图

如果ware里没有信号可以右键->add wave添加,然后设置运行时间5ms,点击run,就会显示波形。

可以看到分频器正确运行,输出频率是输入频率的一半。

-

点击下载

solidwork

行业软件|4.28G

更新时间:2024-10-23

-

点击下载

开博商贸管理系统

行业软件|13.3 MB

更新时间:2023-08-30

-

点击下载

智慧门户电信客户端

行业软件|100.66 MB

更新时间:2023-07-06

-

点击下载

AnyDesk远控

行业软件|3.80MB

更新时间:2023-01-28

-

点击下载

3DMark12正

行业软件|268.16 MB

更新时间:2023-01-13

-

点击下载

北京潭柘寺 V3.

行业软件|34.6 MB

更新时间:2023-01-12

-

点击下载

teamviewe

行业软件|33.66MB

更新时间:2023-01-09

-

点击下载

天师建筑资料管理软

行业软件|27.93 MB

更新时间:2023-01-09

-

点击下载

联想Office激

行业软件|7.75MB

更新时间:2023-01-06

-

点击下载

Camtasia

行业软件|3.50MB

更新时间:2023-01-04