中国科学家的1nm晶体管设计 惊艳了全世界

编者按

在不久之前,我们曾披露,复旦大学微电子学院的周鹏教授,包文中研究员及信息科学与工程学院的万景研究员,创新地提出了硅基二维异质集成叠层晶体管技术。

该技术利用成熟的后端工艺将新型二维材料集成在硅基芯片上,并利用两者高度匹配的物理特性,成功实现4英寸大规模三维异质集成互补场效应晶体管。

该技术成果的文章发表在nature electronics,并受到大家广泛关注。在这里,我们把文章全文翻译,供大家参考。

引言

大规模集成电路的特征尺寸缩小依赖于新型材料、器件架构和工艺流程的持续创新,大数据和即时数据的传输逐渐成为信息技术发展的主要趋势。

目前已经提出了诸如鳍型场效应晶体管(FinFET)、全栅(GAA)以及垂直堆叠的叉片和CFET器件等巧妙的器件架构,缩小晶体管的尺寸可增加集成密度并提高性能。其中,CFET架构(PMOS和NMOS器件垂直堆叠并由同一公共栅极控制)已被证明可以减少42-50%的面积,性能提高7%,与传统的互补金属氧化物半导体(CMOS)器件相比,成本降低了12%10。

因此,它提供了将摩尔定律进一步扩展到1nm节点以下的巨大应用前景。

最近,Intel公司报道的3D堆叠GAA n/p-Si纳米带CMOS展示了最先进的Si工艺技术,其显示出高集成密度和优异的短沟道控制能力。这种3D/3D堆叠CFET架构是硅器件中的一个了不起的突破。

然而,硅基的CFET面临许多制造挑战,例如复杂的工艺流程、对热预算的额外要求、源极和漏极外延生长的困难以及电子/空穴迁移率失配和阈值电压(VTH)调谐的补偿。为了通过双金属栅极调整阈值电压,不可避免地需要额外的光刻、蚀刻和沉积工艺,这使得工艺相当复杂。

在电子器件中使用二维半导体的研究已经开始从单一器件的工作过渡到IC的开发。然而,在将二维系统引入IC行业之前,仍有许多挑战需要解决,包括晶圆级制造、性能匹配、,将2D半导体并入硅互补金属氧化物半导体基IC是一种替代方法,可用于弥合新兴材料与工业应用之间的差距。然而,这需要与传统硅技术兼容的2D材料的器件架构和集成方法。

在本文中,我们提出了一种异质CFET架构,它结合了晶圆级绝缘体上硅(SOI)pFET和二硫化钼(MoS2)nFET。SOI技术自然能够抑制短沟道效应(SCE),降低寄生电容,并具有优异的亚阈值特性和与现代硅工艺的完全兼容性,全耗尽SOI(FD-SOI)技术已经用于先进的VLSI电路,低至22 nm和14 nm技术节点。

另一方面,2D半导体在超大规模CMOS、光电子和传感器中显示出良好的潜力由于其原子厚度、丰富的带结构和高的表面与体积比。MoS2中的电子迁移率与硅中的空穴迁移率相似,可以使用化学气相沉积(CVD)在晶片规模上合成高质量的MoS2,并在低温下转移。

我们通过迁移率匹配(具体地,通过选择MoS2层的厚度)缓解nFET/pFET中电子和空穴之间的迁移率失配问题,堆叠的n/p金属栅极,并引入额外的控制栅极。

我们使用该方法创建了一个SOI–MoS2CFET反相器,在电源电压(VDD)为3V时电压增益高达142.3,在100 mV的低VDD时电压增益为1.2,功耗为64 pW。我们还通过开发SOI–MoS2CFETs的4英寸制造工艺来验证该方法的制造潜力。

1.基于SOI的CMOS工艺平台研发

1.1 器件结构

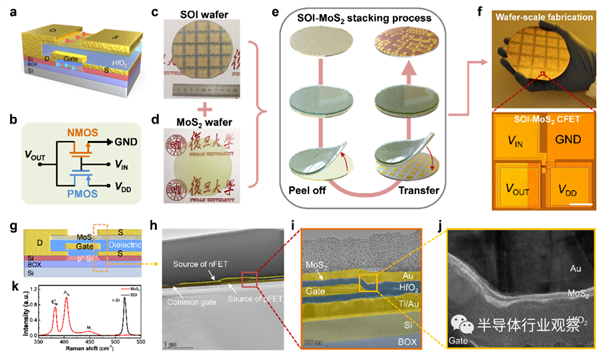

图1a显示了CFET的示意性3D器件结构,其中顶部MoS2用作n沟道,SOI中底部p掺杂Si用作p沟道。图1b给出了相应的等效电路图。

nFET和pFET共享相同的栅极,并且它们的源极通过金属互联。连接的pFET和nFET形成3D集成CMOS反相器。公共栅极用作输入端口,nFET和pFET的连接漏极用作输出端口。

此外,pFET和nFET的源极分别用电源电压(VDD)和GND偏置。两个晶体管的另一端通过电介质层电隔离。由于这种3D堆叠结构,集成密度可以显著提高。图1c和d分别显示了转移工艺之前的4英寸SOI晶片和4英寸MoS2晶片,该晶片具有制造的底部pFET阵列。

图1e是晶圆级MoS2薄膜转移过程的示意图,其中整个4英寸MoS2从初始蓝宝石衬底上剥离并转移到SOI衬底上。MoS2的生长需要相当高的温度(650℃),但是转移过程的温度非常低(130℃),这对底部Si器件的退化可以忽略不计。

这种低温转移工艺也与传统Si CMOS工艺流程中的BEOL工艺完全兼容。图1f是光学显微镜下3D堆叠SOI- MoS2和放大CFET单元的制造晶片。

图1g显示了CFET的横截面示意图。具有不同放大倍数的橙色点矩形区域的相应横截面TEM图像如图1h-j所示。如图1h中的低倍率图像所示,可以观察到堆叠结构,从上到下的三个暗黑色层分别对应于nFET的源极、公共栅极和pFET的栅极。

图1i显示了图1h中深橙色矩形区域的伪着色堆叠结构,清楚地显示了nFET和pFET的金属接触区域以及中间公共栅极。此外,还可以观察到接触区处的MoS2和Si以及两个连接的栅极氧化物(HfO2)层。

图1j显示了图1i中黄色矩形区域的放大图像。在nFET的接触区,观察到具有明显层状结构的三层(3L)MoS2。图1k中的拉曼光谱显示了MoS2的三个特征峰,平面内振动模式位于381.8 cm-1,平面外振动模式位于405.0 cm-1,M1模式位于450.1 cm-1。E2g和A1g之间的频率差约为23.2 cm-1,对应于3L- MoS2,这与TEM表征的结果一致。

此外,对于SOI,位于517.9 cm-1的拉曼峰归因于晶体Si,这表明了SOI衬底中顶部Si的结晶特性。

图 1 3D堆叠CFET的示意图和特性。a、 SOI-MoS2异质3D堆叠CFET的示意图,其中MoS2用作nFET的沟道,SOI晶片的顶部p-Si用作pFET的通道,HfO2作为nFET和pFET两者的高k电介质层。中间栅极充当nFET和pFET共享的公共栅极。

b、 相应的等效电路图。c、 SOI和d. MoS24英寸晶片的光学图像。e、 在SOI衬底顶部转移MoS2的晶圆级工艺。

f、 MoS2转移后3D堆叠CFET晶片的光学图像和CFET器件的放大图像(比例尺:50μm)。g、 a中3D堆叠CFET的横截面示意图。h、3D堆叠CFET结构的横截面扫描透射电子显微镜(STEM)图像。

i、深橙色矩形中堆叠区域的放大伪着色图像j、i中黄色矩形中的放大图像。k、nFET沟道中获得的少数层MoS2的归一化拉曼光谱,以及pFET沟的拉曼峰

1.2 工艺流程与器件制备

SOI基pFET的制造。使用具有100nm厚的顶部Si层和145nm BOX(SiO2)的SOI来制造pFET。首先,进行光刻和湿蚀刻(TMAH:H2O=2:5体积)以限定有源区和沟道。然后,采用离子注入BF2来形成有源区的p+掺杂,随后在950°C下进行快速热退火以激活。

使用电子束蒸发器(EBE)在有源区上的金属沉积(Ti/Au:20nm/80nm)来形成源极/漏极接触,然后在300°C下快速热退火10分钟以获得更好的接触性能。随后,通过ALD沉积20nm HfO2,通过EBE沉积60nm Au,分别形成栅极电介质和栅极电极。

晶圆级MoS2的合成。使用典型的CVD工进行单层MoS2生长。通常,将4英寸蓝宝石衬底置于石英管的下游。将MoO3粉末(Alfa Aesar,99.95%)和硫粉末(Alpha Aeser,99.999%)置于不同的温度控制区域。在650°C和180°C下用氩气作为载气分别加热粉末后,最终在大气压下在10分钟硫化时间内在蓝宝石衬底上获得连续的1L- MoS2薄片。

晶圆级MoS2的转移。在晶圆级的MoS2单独合成后,进行CVD 1L- MoS2逐层堆叠,以获得特定数量的MoS2,然后在给定的基底上真空转移少量MoS2,分别旋涂到合成的4英寸MoS2/蓝宝石衬底上,并在180°C下对每层光致抗蚀剂进行3分钟的背衬。

其次,将热释放带(TRT)牢固地附着在光致抗蚀剂的表面上,将制成的TRT/光致抗蚀剂/ MoS2/蓝宝石样品在室温下浸入去离子水中10分钟。

然后从去离子水中取出样品,并将TRT/光刻胶/ MoS2层从蓝宝石衬底上机械剥离。第三,然后将具有TRT/光致抗蚀剂的第一层MoS2(L1)堆叠并压在蓝宝石样品上的下一合成裸MoS2的顶部,然后重复上述浸渍和剥离过程以获得双层MoS2。

然后通过重复第三步骤获得具有TRT/光致抗蚀剂的三层MoS2。第四,通过在130°C下加热30分钟以释放TRT,在真空转移室中将带有TRT/光致抗蚀剂的三层MoS2转移到靶向4英寸SOI衬底上。

最后,将MMA/PMMA光致抗蚀剂依次在丙酮和异丙醇中洗掉,然后将4英寸3L- MoS2/SOI样品在真空(~10-3Pa)下在200°C下退火2小时,以提高转移的MoS2和SOI衬底之间的粘附力。

2.器件的电学表征结果

2.1 SOI- MoS2-CFET电特性显示出高性能

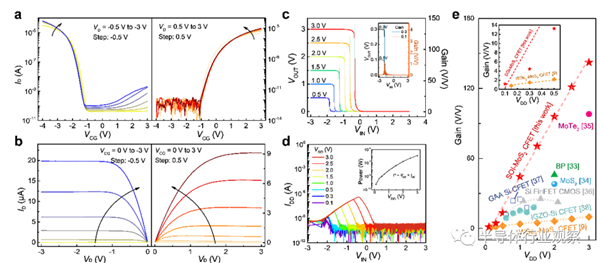

在本工作中,我们对制备出的器件进行了电学测量表征,并提取出关键的参数,包括开态电流、开关比和亚阈值摆幅等。图2a、b显示了具有相同沟道尺寸的代表性nFET和pFET器件的传输和输出特性,其中沟道宽度和长度分别为10μm和16μm。n型(MoS2)和p型(p-Si)晶体管通过中间公共栅极显示出优异的可控性。

当公共栅极(VCG)的电压从-4V扫描到+3V时,MoS2nFET的漏极电流(ID)在室温下在0.5V漏极偏置(VD)下从约1pA增加到3.43μA,而SOI pFET的从31.7μA降低到45pA。nFET和pFET的ION/IOFF电流比分别为3.43 x 106和7.04×105。此外,通过Y函数方法提取场效应迁移率μFET, nFET和pFET的提取μFET分别为33 cm? V-1s-1和85 cm?V-1s-1。

此外,nFET和pFET的亚阈值摆幅(SS)分别为160.4mV/dec和147.8mV/dec。通过减小栅极氧化物和沟道的厚度可以进一步改善SS。如图2b中的ID-VD特性所示,这两种器件都显示出良好的输出饱和,并伴有合格的跨导,这对于进一步提高反相器和电路的增益,从而提高噪声容限非常重要。

图2c显示了作为输入电压(VIN)函数的CFET反相器的电压传输特性和相应的电压增益,电源电压(VDD)范围为0.5 V至3.0 V。当VIN为低(逻辑“0”)时,输出电压(VOUT)为高(逻辑“1”),当VIN增加(逻辑“2”)时VOUT被下拉至低电平(逻辑“3”),展示了逻辑反相器功能。VDD附近的高VOUT和0.1mV附近的低VOUT表明两个FET之间的良好电压匹配及其低漏电流。

电压增益随着VDD的增加而增加,并且在VDD=3V时达到142.3V/V的峰值。此外,过渡电压(VM)显示出朝向正VIN的右移趋势。为了降低电路的功耗,需要降低VDD。

因此,还研究了VDD缩小时反相器增益的变化。图2c的插图显示了CFET反相器在300 mV和100 mV的低VDD下的电压传输特性。在100 mV最小VDD下,逆变器产生1.2 V/V的增益,这是确保反相器工作的众所周知的基准,显示了我们的CFET在超低电压应用中的潜力。

据我们所知,这里报道的这种超低工作电压从未被报道用于基于2D半导体的3D集成电路。此外,这种用于电路操作的超低电源电压也与成熟的Si CMOS技术中的创纪录低水平相当。

低电源电压对于降低电路功耗至关重要。CFET反相器的静态电流(IDD)和静态峰值功耗如图2d所示。随着VDD的降低,IDD显著降低。静态功耗由P=VDD×IDD定义,并在过渡区达到峰值。如图2d插图所示,VDD从3 V降低到100 mV导致功耗降低约1.9×104倍。100 mV VDD下的功耗仅为64 pW,这是基于2D TMD的反相器的最佳报告值之一。

作为VDD函数的电压增益与其他工作的比较如图2e所示。我们的CFET反相器具有优异的增益和低电压操作能力。我们的器件的反相器增益比基于MoS2电阻器的nMOS反相器或其他基于MoS2的异质CMOS反相器的增益高几倍,并且在每个VDD处都是最高值。

此外,与2D-2D集成CFET(橙色虚线)相比,我们的反相器增益在每个VDD处都要高得多,在3V的VDD处大约高14.5倍。插图显示了VDD<0.5V时的细节,我们的反相器在创纪录的低VDD(100mV)下显示出高增益。除了优异的开关性能外,与基于其他2D材料的CFET相比,我们的CFET反相器还具有晶圆级集成能力。

一方面,SOI技术已经成熟,并在现代集成电路中被广泛采用。另一方面,具有可控厚度的晶圆级转移CVD MoS2非常适合大面积集成,并且由于其低热预算转移工艺,与现代硅工艺完全兼容。

图 2顶层nFET和底层pFET以及异质CFET反相器电学性能。a、 MoS2nFET和SOI pFET的ID-VCG传输特性。b、 MoS2nFET和SOI pFET的ID-VD输出特性。

c、 在VDD=0.5V-3.0V下,CFET反相器的电压传输特性和增益,插图显示了在极低VDD=0.3V和0.1V。d、CFET反相器工作的情况。插图显示了峰值功耗随着VDD的降低而降低。

e、先进硅基CFET和2D半导体基逻辑反相器在不同电源电压下的电压增益比较。插图显示了低电源电压时的特写。

2.2 SOI-MoS2CFET中的nFET/pFET平衡问题和解决方案

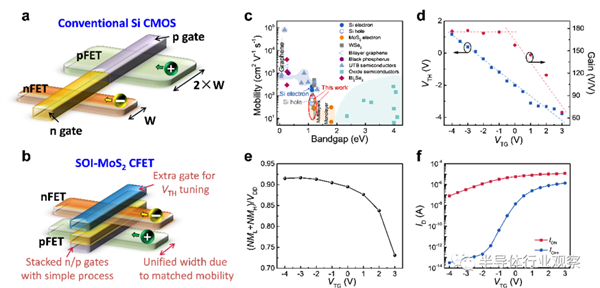

CMOS电路的操作要求nFET和pFET在驱动能力和漏电流方面保持平衡。Si中的电子迁移率远高于空穴迁移率。为了补偿迁移率差异,pFET的宽度通常是nFET的两倍,以平衡传统Si CMOS中的nFET/pFET驱动能力,如图所示。这降低了电路集成密度。

另一方面,nFET和pFET的VTH也应匹配,以便具有可比较的漏电流和On/OFF电流比。在传统的Si-CMOS中,这通常通过在nFET和pFET中使用不同的金属栅极材料来实现,这需要多次光刻和复杂的工艺步骤。

与传统的Si CMOS相比,SOI-MoS2CFET具有更好的nFET/pFET平衡能力。多层MoS2和Si之间的载流子迁移率和能带隙很好地匹配,如图3c所示。

根据最近的报告,多层MoS2的电子迁移率约为10-100 cm? V-1s-1,这与Si沟道中的空穴迁移率匹配,并确保了兼容的驱动电流。顶部使用氧化物半导体的CFET是一个有趣的替代方案,因为氧化物半导体的直接沉积可以简化工艺。

然而,考虑到带隙、迁移率和MoS2晶体管的缩放能力的匹配,我们工作中提出的Si- MoS2是先进技术节点最有吸引力的解决方案之一。此外,我们的CFET架构可以显著减少SOI- MoS2CFET中的器件面积并提高集成密度,因为nFET和pFET中的宽度是统一的,如图3b所示。此外,用于VTH调谐的nFET和pFET中的不同金属栅极可以通过具有单个光刻步骤的3D堆叠工艺方便地形成。

SOI- MoS2CFET中用于平衡nFET和pFET的额外栅极(VTG)位于MoS2nFET通道顶部,见图3b。分别沉积20nm HfO2和40nm Au作为栅极电介质和栅极电极。通过改变VTG,可以通过界面耦合效应来调制顶部MoS2nFET的VTH。图3d显示,随着VTG从-4V增加到3V,MoS2nFET的VTH从1.2V降低到-3.8V。由于n/pFET平衡更好,nFET VTH的调制将反相器的增益进一步提高到177.2V/V。

通过VTH的调谐,反相器的噪声容限也显著提高。图3e显示,随着VTH从3V变为-4V,CFET的总噪声容限从73.1%提高到91.5%。大的噪声容限有利于CFET在低电源电压下的可靠操作。额外的栅极还可以用于在高操作速度和低功耗模式之间切换电路。这是通过VTG调制MOSFET的导通和截止状态电流来实现的。

随着VTG从-4V增加到3V,导通状态电流从80.7 nA上升到11.5μA,工作频率更高,如图3f所示。这种情况的折衷是断开电流增加,导致更高的功耗。SOI的全局背栅(VBG)也可用于调制pFET的VTH,类似于传统SOI CMOS中的VTH。可以将VBG和VTG的使用结合到CFET的操作中,以进一步提高性能。

图3.SOI-MoS2CFET在nFET/pFET平衡方面的优势。a、 b。比较传统Si CMOS(a)和SOI-MoS2异质CFET(b)的示意图。c、各种2D材料、超薄体(UTB)半导体和氧化物半导体之间的能带隙和载流子迁移率的比较。d、 VTG对nFET的VTH和反相器增益的调制。

e、 VDD=3 V 时,VTG对反相器噪声容限的影响。f、VTG对nFET导通和截止状态电流的调制。

3. MoS2/ Si作为“一步”光电系统的应用

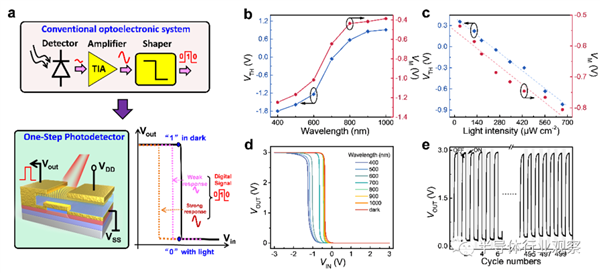

SOI-MoS23D堆叠结构也可用于其他应用。结合暴露的MoS2的高量子效率和反相器的高增益,SOI- MoS2CFET可以将具有不同强度和波长的光信号直接转换为数字电信号。在传统的光电子系统中,使用多个组件来实现这种功能,如图4a所示。

入射光信号首先由光电检测器(PD)转换成电信号。之后,弱电信号由跨阻抗放大器(TIA)增强。TIA的输出通常是模拟信号,其振幅受到光强度和波长的强烈影响。波形整形器还用于将该模拟信号转换为数字信号。

使用SOI- MoS2CFET,光信号直接转换为数字信号,而不受强度和波长的影响。这是通过MoS2的高量子效率和SOI- MoS2CFET的高增益实现的,如图4a所示。在照明下,由于光诱导栅极效应,暴露的MoS2沟道显示出负的VTH偏移。MoS2nFET的VTH位移强烈地由光强度和波长决定,并且由于更强的吸收系数,在更短的波长下更明显,见图4b。

相反,具有长波长的光在薄MoS2膜中的吸收较差,因此引起较少的VTH偏移。VTH上的光强度调制类似。随着光强度的增加,由于更强的光诱导栅极效应,VTH降低得更多,如图4c所示。

MoS2nFET中VTH的偏移导致SOI- MoS2CFET反相器中VM的偏移。图4d显示了反相器在各种光波长下的VIN-VOUT曲线。在较短的波长下,由于下拉晶体管(nFET)的更强驱动能力,VM的负偏移更大。

当用作“一步”光电子器件时,SOI- MoS2CFET的公共栅极被偏置在VM附近,VM位于反相的边缘。如图4a下图所示,随着VM的轻微降低,反相器的输出从“1”下降到“0”。由于反相器的高增益,逻辑状态的转换发生在强光或弱光响应下。

如图4e所示,CFET的偏置电压为VIN=-500 mV,VDD=3 V。选择VIN值是为了将反相器的VOUT设置为高电平,并在黑暗中靠近VM。当灯周期性地打开和关闭时,VOUT周期性地分别变为低逻辑电平和高逻辑电平,电压摆动较大。

结果证实,我们的设备可以一步将光信号转换为数字信号。与传统的光电系统相比,这种“一步”的装置更为紧凑和经济。更进一步,我们还证明,我们的SOI- MoS2异质CFET可以进一步用作气体传感器,以检测NO2和NH3,因为MoS2和Si对这种氧化气体和还原气体具有高灵敏度。

图4.SOI- MoS2-CFET作为“一步”光电器件的应用。a、将传统光电系统与SOI -MoS2- CFET作为一步光电探测器进行比较的示意图。b、在669μW cm-2的恒定光强下,不同波长(1000 nm-400 nm)对MoS2nFET的VTH的影响。

c、 固定波长为700 nm的不同光强度(暗-669μW cm-2)对MoS2nFET的VTH的影响。d、 在669μW cm-2的恒定光强下,不同波长(1000 nm-400 nm)对SOI- MoS2逆变器传输特性的影响。

e、 SOI- MoS2CFET反相器的输出波形显示在光脉冲下具有大电压摆动的数字信号。

4.结论

在本项目中,我们报道了一种包含SOI基pFET和MoS2基nFET的3D堆叠异质CFET。我们的SOI–MoS2CFET反相器在VDD=3 V时的电压增益为142.3,这优于基于全硅CMOS或全2D材料的报道的CFET。

在VDD=100 mV时,我们的CFET显示出1.2的电压增益和低至64 pW的功耗,使其在低功耗应用中具有竞争力。SOI–MoS2CFET还提供了灵活的nFET/pFET平衡能力,具有良好匹配的迁移率、用于堆叠n/p金属栅极的简单工艺以及用于VTH调谐的额外顶栅。我们的CFET还可以用于制造紧凑的一步光电系统,其中光信号在单个设备内直接转换为电数字信号,以及用于检测NO2和NH3的气体传感器。

另一方面,我们还开发了一种4英寸晶圆级集成技术,该技术将成熟的SOI工艺与CVD生长的MoS2的低温转移相结合。SOI技术由于其缩放能力,已广泛应用于先进的超大规模集成(VLSI)电路中。

因此,我们的SOI–MoS2异质集成方法可用于开发具有高3D面积效率、低加工难度、低功耗和新颖功能的商用器件,并为将2D半导体从实验室过渡到业界提供了一条实用途径。

| 今天推荐游戏软件~ | |||

| 橙光游戏 | |||

| 竹本无心 | 她等待刀尖已经太久 | 白痴做梦 | 闲云寄人间 |

| 手机软件 | |||

| 趣团购 | 西柚小说 | 番茄todo季度卡破解版 | 番茄严选正版 |

| 单机游戏 | |||

| 彩虹六号:封锁 免费版 | 怪物猎人物语2 | 使命召唤9:黑色行动2 | 红色警戒2尤里的复仇 |

| 电脑应用 | |||

| 腾讯交互翻译 | Office自动保存工具 | 迅游加速器 | 护眼吧v1.0.0.1 |

推荐阅读

更多>- 06-13独特港漫风 不一样的西游龙神八部之西行纪6月5日全平台上线!

- 05-25已有超百万玩家将收获日3加入愿望清单 开发已接近尾声

- 12-19成本上天了 消息称三星3nm良率仅有20%:急找美国援助

- 12-14AOC 新款 Q27G3ZE 显示器-2K 240Hz-首发 1999 元

- 12-13小米MIX Fold 2新配色预售抢光:顶配卖11999元

- 12-12DNF:最受欢迎的4大职业出炉!肥宗实至名归,女气功遗憾落榜

- 12-12使命召唤手游恶魔之息传说级武器上线;TGA2022获奖名单公布

- 12-12王者荣耀:世冠中国队碾压外国队,又是一次自嗨比赛?

- 12-122大LPL选手公开求职!Angel认错:过去太保守!绿毛:不想转幕后

- 12-09TGA22:曝2077将展示付费扩展“往日之影”内容